e-ISSN: 2319-8753 | p-ISSN: 2347-6710

DIA

International Journal of Innovative Research in SCIENCE | ENGINEERING | TECHNOLOGY

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

Volume 13, Special Issue 1, April 2024

INTERNATIONAL STANDARD SERIAL NUMBER INDIA

# Impact Factor: 8.423

9940 572 462

6381 907 438

🖂 ijirset@gmail.com

International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization Volume 13, Special Issue 1, April 2024

11<sup>th</sup> National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24) 25<sup>th</sup> - 26<sup>th</sup> April 2024

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# **RTL Verification of Scrambler and Descrambler for Data Communication**

Mr. P. Gurusamy<sup>1</sup>, M.E., T. Jerolin<sup>2</sup>, V. Kavya<sup>3</sup>, D. Lavanya<sup>4</sup>, A. Mahalakshmi<sup>5</sup>

Assistant Professor, Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering,

Krishnagiri, Tamil Nadu, India<sup>1</sup>

U.G Scholars, Department of Electronics and Communication Engineering, Adhiyamaan College of Engineering,

Krishnagiri, Tamil Nadu, India<sup>2,3,4,5</sup>

**ABSTRACT**: Data security and integrity must be guaranteed in contemporary data transmission systems. This is commonly accomplished by the use of scramblers and descramblers, which provide controlled unpredictability to the sent data. The Register Transfer Level (RTL) verification of a scrambler and descrambler design for data communication applications is the main emphasis of this study. Verifying the performance, resilience, and functional correctness of the implemented scrambler and descrambler RTL designs is the main goal of this research. To make sure the designs adhere to the required specifications and standards, the verification process entails extensive testing using formal verification techniques and simulation.

**KEYWORDS:** RTL design implementation, Scrambler, Descrambler, Linear feedback shift register, Formal verification.

# I. INTRODUCTION

Information must be transmitted reliably, securely, and efficiently in the context of contemporary data communication systems. In order to achieve these goals, scramblers and descramblers are essential because they improve data security and integrity by adding controlled randomness to the sent data. The goal of this project is to verify a scrambler and descrambler design suited for data communication applications at the Register Transfer Level (RTL). Different encoding and modulation techniques are used by data communication systems to transfer information across channels. Before data is transmitted, scramblers are used to add controlled randomness to the stream. Descramblers then reverse this process at thereceiving end to recover the original data. By reducing problems like data reliance, signal distortion, and interference susceptibility, this scrambling and descrambling procedure ensures more dependable and resilient communication.

# **II. RELATED WORKS**

For data transmission projects, RTL (Register Transfer Level) testing of a scrambler and descrambler entails confirming the accuracy of the hardware description of these modules. Usually, this entails building testbenches to stimulate the RTL code's inputs and observing the outputs to make sure they correspond to expected behaviour. Furthermore, the design canbe simulated and its validity confirmed using RTL simulation tools such as ModelSim or Cadence Incisive. To mimic the behaviour of the RTL designs, use simulation tools such as ModelSim. To create stimulation and compare the output to anticipated outcomes, create test benches. Make sure the testbench exercises every aspect of the design by using coverageanalysis.

# **III. EXISTING METHOD**

In the current data transmission system, data is usually transmitted without being first scrambled or descrambled. This

ISSN (Online) : 2319 - 8753 ISSN (Print) : 2347 - 6710

Volume 13, Special Issue 1, April 2024

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

# 25<sup>th</sup> - 26<sup>th</sup> April 2024

# Organized by

### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

indicates that there is no encoding or decoding involved and the data is transmitted in its original format. Data communication systems require a scrambler and descrambler solution since the current technique is insecure, unreliable against noise, incompatible with data, and inefficient with bandwidth.

### **IV. PROPOSED SYSTEM**

Implementing and validating an RTL-level descrambler and scrambler for data transfer is part of the suggested system. Prior to transmission, the data is encoded by the scrambler and decoded upon receiving by the descrambler. During transmission, this procedure guarantees data security, integrity, and dependability. In comparison to the current system, the suggested system provides better security, noise immunity, data integrity, and bandwidth utilisation, making it a strong option for data transmission applications.

### V. BLOCK DIAGRAM

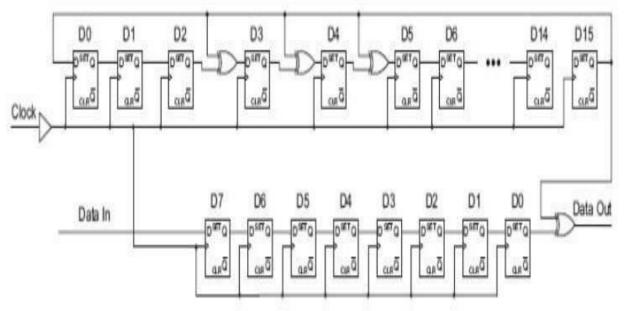

In order to verify that a scrambler and descrambler for data communication are operating correctly at the Register TransferLevel (RTL) of hardware description, this process is known as RTL verification. In this procedure, the original data is encoded using a particular algorithm by the scrambler, producing scrambled data. After then, the data is jumbled and sent over a communication channel. The original data is recovered from the received scrambled data by the descrambler, which reverses the encoding process at the receiving end. The accuracy of the descrambler is confirmed by comparing the recovered data with the original input. A successful match verifies that the encoding and decoding procedures were efficient, guaranteeing safe and dependable data transfer.

```

Here is an example of a scrambler with the polynomial G(x) = x^{16}+x^5+x^4+x^3+1

```

Fig 1. Block diagram for proposed method

The scrambler takes the input data and jumbles it using a preset algorithm. This may involve XORing the input data with a pseudorandom sequence produced by a polynomial function. This can be demonstrated with a block diagram that

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization Volume 13, Special Issue 1, April 2024 11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

24) 25<sup>th</sup> - 26<sup>th</sup> April 2024

# Organized by

#### Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

shows the XOR gate, the pseudorandom sequence generator, and the input data. Each block can be represented by a simple logic

gate or by programmable logic devices like FPGAs (Field-Programmable Gate Arrays). The descrambler operates in the opposite manner from the scrambler. It takes the jumbled data and puts it back in its original format. Typically, it involvesusing the same pseudorandom sequence generator to XOR the jumbled data. Again, this could be shown with a block diagram similar to the scrambler circuit. Real-Time Interface (RTI) verification is the process of examining these circuits' performance under real-time conditions. To accomplish this, feed the known input data into the scrambler, observe the resulting scramble, feed it into the descrambler, and verify that the output matches the original input. A test bench that provides multiple input patterns and compares the output to the intended results can be constructed to automate this process.

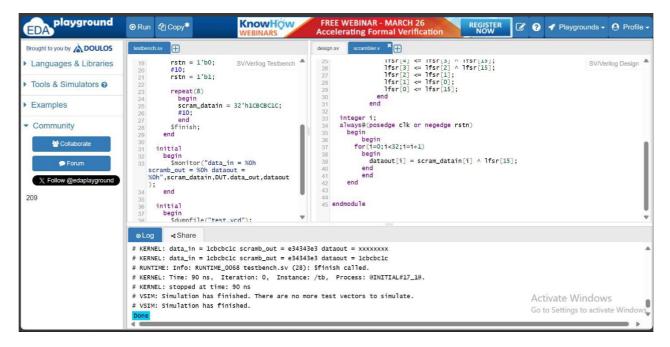

# VI. EXPERIMENTAL RESULTS

The scrambling efficiency, throughput, and resource usage of the scrambler module can all be used to assess its performance. First, by comparing the quality of the scrambled output to the original data, the efficacy of the scrambler canbe evaluated. Analysing statistical characteristics like the output signal's autocorrelation and frequency spectrum will helpachieve this. A good scrambler should spread the signal's energy over a larger frequency range to increase privacy and make the signal more resistant to interference. Second, the module's throughput can be monitored to make sure it satisfies the communication system's requirements. This entails figuring out the maximum data rate the scrambler can achieve in various operating scenarios while taking data width and clock frequency into account. Finally, the module's resource usage needs to be assessed to see if it can be implemented on the intended hardware platform. This entails examining metrics likemaximum clock frequency, memory usage, and logic utilisation to make sure the module can be incorporated into the overall system architecture without going over resource limits. In general, the project's experimental findings will shed light on the functionality and performance of the scrambler module for data communication applications.

Fig 3. Expected result

ISSN (Online) : 2319 - 8753 ISSN (Print) : 2347 - 6710

#### International Journal of Innovative Research in Science, Engineering and Technology An ISO 3297: 2007 Certified Organization Volume 13, Special Issue 1, April 2024

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

25<sup>th</sup> - 26<sup>th</sup> April 2024

Organized by

Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

# VII. FUTURE SCOPE

This project's future scope includes a wide range of possible developments and uses in the data communication industry.Optimising the design for FPGA or ASIC implementation with an emphasis on improving power consumption, timing performance, and resource efficiency is one path of investigation. Furthermore, by including error detection and correction mechanisms in the scrambler, the system's resistance to noise and channel distortions may be strengthened, leading to an increase in overall data reliability. Security improvements could be made to strengthen data integrity and confidentiality during transmission, such as implementing cryptographic algorithms. The ability to customise for particular communication standards, like Ethernet or USB, offers the chance to adjust parameters like polynomial selection and data width in order to meet industry-specific requirements. Moreover, improving simulation and verification techniques by creating thorough testbenches would guarantee the design's resilience and dependability in a range of operational scenarios. Investigating different methods of data scrambling, like block cyphers or chaotic maps, might reveal creative strategies with possible performance advantages. Ultimately, testing and evaluation in the real world would be made possible by integrating the scrambler and descrambler modules into more extensive communication systems or networks. This would provide insights into the modules' scalability and interoperability within intricate communication infrastructures. These directions for the future show promise in terms of improving data communication technologies, tackling new issues, and opening up fresh doors for impact on the industry and innovation.

### VIII. CONCLUSION

In order to guarantee the confidentiality, integrity, and dependability of data transmission systems, the scrambler and descrambler for data communication must undergo RTL verification. Potential problems and weaknesses in the design can be found and fixed before deployment through thorough testing and verification, reducing the chance of data breaches and communication breakdowns. Through the implementation and verification of scrambler and descrambler modules at the RTL level, enterprises can construct resilient and safe data communication metworks that are able to protect confidential data in a variety of industries and applications. Furthermore, the verification method makes it possible for the design to be optimised and improved continuously, guaranteeing that it satisfies the changing demands and difficulties of contemporarycommunication technologies.

#### REFERENCES

- 1. K.M.L Sai Indrani and P. Ramesh, "A Study on the Performance of an AWGN Channel in a Communication System," International Journal of Electronics & Communication Technology, Vol. 4, Issue 2, pp. 89–90, June 2013.

- 2. ," How ITU's Broadband Standards Improve Access to the Internet," [online] available at http://www.itu.int/osg/spu/ip/chapter\_seven.html [accessed, June, 2017]

- 3. N. Vlajic, "Digital Transmission of Digital Data: Line and Block Coding, Digital Transmission Modes," course material, 2010.

- 4. N. Jiping, Z. Yongchuan, H. Zhihua, and Y. Zuqiao, "A Digital Image Scrambling Method Basedon AES and Errorcorrecting Code," International Conference on Computer Science and Software Engineering., pp. 677–680, 2008.

- 5. Rohith S., K. N. H. Bhat, and A. N. Sharma, "Image Encryption and Decryption using Chaotic Key Sequence Generated by Sequence of Logistic Map and Sequence of States of Linear Feedback

- 6. Shift Register," International Conference on Advancein Electronics, Computers andCommunications, 2014.

- D. S. Bhojane, S. S. Oak, and A. S. Joshi, "Design of Logical Scrambling and De-Scrambling System for High Speed Application," International Conference on Computing for Sustainable Global Development, pp. 617-622, 2016.

- 8. S. T. Allawi and J. H. Al-A'meri, "Image Encryption Based on Linear Feedback Shift Register Method," Al-Sadeq International Conference on Multidisciplinary in IT and Communication Scienceand Applications, 2016.

- 9. J. A. Sheikh, Uzma, S. A. Parah, and G. M. Bhat, "Bit Error Rate (BER) Improvement of Multiple Input Multiple Output Orthogonal Frequency Division Multiplexing (MIMO-OFDM) System Using Bit Level Scrambling,"IEEE

Volume 13, Special Issue 1, April 2024

# International Journal of Innovative Research in Science, Engineering and Technology

An ISO 3297: 2007 Certified Organization

11th National Conference on Frontiers in Communication & Signal Processing Systems (NCFCSPS '24)

25<sup>th</sup> - 26<sup>th</sup> April 2024

# Organized by

# Department of ECE, Adhiyamaan College of Engineering, Hosur, Tamilnadu, India

INDICON, 2015

- 10. K. Amandeep, "Linear Feedback Shift Registers in Wireless Communication Systems," India : Thapar Institute of Engineering and Technology, 2006.

- 11. F. Masoodi, S. Alam, and M. U. Bhokari, "An Analysis of Linear Feedback Shift Registers in Stream Ciphers," International Journal of Computer Applications Volume 46, No.17, pp 46-49, May2012.

# BIOGRAPHY

Mr.P.Gurusamy.,M.E.,Assistant Professor, Department of Electronics and CommunicationEngineering, Adhiyamaan college of Engineering, Hosur.

Jerolin T Department of Electronics and CommunicationEngineering, Adhiyamaan college of Engineering, Hosur

Kavya V Department of Electronics and CommunicationEngineering, Adhiyamaan college of Engineering, Hosur.

Lavanya D Department of Electronics and CommunicationEngineering, Adhiyamaan college of Engineering, Hosur.

Mahalakshmi.A Department of Electronics and CommunicationEngineering, Adhiyamaan college of Engineering, Hosur.

INTERNATIONAL Standard Serial Number India

# INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH

IN SCIENCE | ENGINEERING | TECHNOLOGY

www.ijirset.com